مقاومت پول آپ — از صفر تا صد

مقاومت پول آپ یا بالاکش (Pull-up) و پول داون یا پایینکش (Pull-down) معمولا برای بایاس صحیح ورودی گیتهای دیجیتال استفاده میشوند. در واقع این مقاومتها زمانی که ورودی وجود نداشته باشد، از شناور ماندن (Floating) و دریافت مقادیر تصادفی (Random) جلوگیری میکنند. در این مطلب قصد داریم به بیان نحوه کار این مقاومتها و کاربردهای آنها در مدارات مختلف بپردازیم.

گیتهای منطقی میتوانند برای اتصال به مدارات و ادوات خارجی مورد استفاده قرار گیرند، اما باید اطمینان حاصل کرد که عملکرد ورودی و خروجی آنها صحیح است و شرایط کلیدزنی بر آنچه از قبل برنامهریزی شده بود، منطبق باشد. گیتهای منطقی دیجیتال مدرن، آیسیها و نیز میکروکنترلرها دارای ورودیهای زیادی هستند که پین نامیده میشوند. همچنین این ادوات دارای یک تا تعداد بیشتری خروجی نیز هستند. برای این که مدار دیجیتال به صورت صحیح کار کند، تمام این ورودیها و خروجیها باید به صورت صحیح (در حالت HIGH یا LOW) تنظیم شده باشند.

میدانیم که گیتهای منطقی، پایهایترین عنصر در ساخت تمام مدارات دیجیتال منطقی هستند. با ترکیب سه گیت پایه AND ،OR و NOT میتوان مدارات ترکیبی بسیار پیچیدهای ساخت. در مدارت دیجیتال، فقط یکی از دو حالت منطقی صفر یا یک میتوانند وجود داشته باشد. این دو حالت منطق صفر و منطق یک نامیده میشوند.

این دو حالت منطقی توسط دو سطح ولتاژ مختلف نشان داده میشوند. در واقع هر ولتاژی که زیر سطح معینی باشد به عنوان منطق صفر و هر ولتاژی که بالای سطح دیگری باشد، به عنوان منطق یک در نظر گرفته میشود. به عنوان مثال اگر دو سطح ولتاژ ۰ ولت و ۵ ولت وجود داشته باشند، در این صورت صفر ولت نشاندهنده منطق صفر و ولتاژ ۵ ولت نشاندهنده منطق یک است.

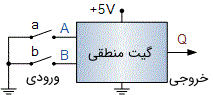

اگر ورودی گیتهای منطقی دیجیتال یا مدارات دیجیتال در بازهای نباشد که بتوان آن را با ورودی منطق صفر و یا منطق یک نشان داد، در این صورت ممکن است مدار دیجیتال دچار تریگر اشتباه شود؛ زیرا گیت یا مدار منطقی نمیتواند مقدار صحیح ورودی را تشخیص دهد. به عبارت دیگر سطح HIGH به اندازه کافی بالا نیست و یا سطح LOW به اندازه کافی پایین نیست. مدار زیر را به عنوان مثال در نظر بگیرید. کلیدهای a و b، ورودیهای یک گیت منطقی عمومی را نشان میدهند.

زمانی که کلید a بسته شده باشد، ورودی A به زمین یا ولتاژ صفر ولت (منطق صفر) متصل است. زمانی که کلید b بسته شده باشد، ورودی B به نیز به زمین متصل میشود. این ورودیها در حالت درست و مورد انتظار هستند. اما اگر کلید a باز باشد، آنگاه وضعیت ورودی A چه خواهد بود؟ آیا این ورودی در منطق صفر (LOW) قرار دارد یا منطق یک (HIGH)؟

اگر ورودی A را در ولتاژ ۵ ولت و منطق یک در نظر بگیریم، آنگاه نشان میدهد که ورودی دیگر به زمین متصل نیست. اما این فرض درست نیست؛ زیرا این ورودی در حالت شناور قرار دارد و به صورت تصادفی ورودی دریافت میکند، به عبارت دیگر این پتانسیل را دارد که در بازه مقادیر بین ۰ و ۵ ولت قرار داشته باشد. دلیل این اتفاق این است که ورودی به صورت موثر برای بودن در هر کدام از دو منطق صفر و یک تعریف نشده است. شناور بودن ورودی به آن اجازه میدهد که در هر سطحی از ولتاژ، هم HIGH و هم LOW، مدار را تریگر کند.

این وضعیت غیرقطعی منجر به این امر میشود که ورودی دیجیتال A در سطح منطقی صفر (LOW) قرار داشته باشد، در حالی که ما زمان باز بودن کلید A، به سطح منطقی یک (HIGH) نیاز داشته باشیم. به همین دلیل گیت منطقی، خروجی Q را به صورت اشتباهی تریگر میکند. حتی اگر در یک بازه زمانی مقدار این ورودی در سطح یک منطقی قرار داشته باشد، سیگنال ورودی ضعیف و متغیر است و میتواند به آسانی مقدار ورودی را با دریافت نویز از مدارات مجاور خود تغییر دهد و یا ورودی را به حالت نوسانی تبدیل کند و گیت منطقی را خراب و یا خروجی آن را غیرقابل استفاده کند. این موارد در مورد کلید b نیز کاملا صادق است و تمام این مشکلات در صورت باز بودن این کلید نیز به وجود میآید.

بنابراین برای جلوگیری از کلیدزنی تصادفی مدارات دیجیتال منطقی، باید تمام ورودیهایی که به جایی متصل نیستند (به آنها ورودیهای شناور گفته میشود) را متناسب با کارکرد مدار، به منطق یک و یا منطق صفر متصل شوند. میتوان این کار را به سادگی و با اتصال پینهای ورودی به مقادیر معین سطح صفر یا سطح یک از طریق مقاومتهای پولآپ و پول داون انجام داد. در این صورت، در تمام موقعیتهایی که کلید باز یا بسته باشد و یا هیچ چیزی به آنها متصل نباشد، مدار ورودی دلخواه کاربر را دریافت میکند.

هنگام ساخت مدارات منطقی دیجیتال، معمولا این وضعیت پیش میآید که از تمام ورودیهای چندگانه آيسیها و گیتهای منطقی و لچها استفاده نمیشود و یا در یک پکیج آیسی، از تمام گیتهای منطقی و لچهای درون آن استفاده نمیشود. در این شرایط، تمام پایههای استفاده نشده باید یا از طریق یک مقاومت با مقدار بالا که به آن مقاومت پولآپ گفته میشود، به ولتاژ منبع تغذیه وصل شوند و یا از طریق یک مقاومت با مقدار کوچک که به آن مقاومت پول داون گفته میشود، به ولتاژ صفر ولت زمین متصل شوند. پایههایی که از آنها استفاده نمیشود، نباید هیچگاه به صورت شناور رها شوند.

مقاومت پول آپ

متداولترین روش برای اینکه اطمینان حاصل شود که ورودیها در مدارات و گیتهای منطقی دیجیتال در حالت خود-بایاس (Self-Bias) یا شناور قرار ندارند، این است که ورودیها را مستقیما برای دریافت سطح صفر منطقی یا ولتاژ ثابت صفر ولت (در گیتهای AND و OR) به زمین و برای دریافت سطح ثابت یک منطقی (در گیتهای AND و NAND) به ولتاژ منبع تغذیه متصل کنیم.

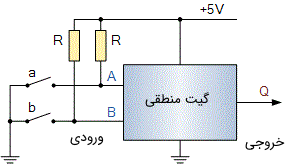

مجددا مدار زیر با یک گیت منطقی و دو کلید در ورودی را در نظر میگیریم.

این بار برای جلوگیری از دریافت مقادیر شناور در ورودیها هنگام باز بودن کلیدهای a و b، ورودیها مستقیما به ولتاژ ۵ ولت منبع تغذیه متصل شدهاند. ممکن است به این صورت تصور شود که حال دیگر مدار مشکلی ندارد و در صورتی که کلیدها باز باشند، ورودیها مقادیر ۵ ولت را دریافت خواهند کرد و گیت عمل کرد مناسبی دارد و نیز هنگام بسته بودن کلید، ورودی به ولتاژ ثابت صفر ولت زمین متصل است و در سطح LOW قرار میگیرد.

اما در واقع، این مدار نیز دارای مشکل در عملکرد خواهد بود؛ زیرا زمانی که هر یک از دو کلید بسته باشند، یک مدار اتصال کوتاه (Short Circuit) بین ولتاژ منبع تغذیه و زمین به وجود میآید. این شرایط باعث میشود که جریان زیادی در مدار جریان یابد و موجب سوختن فیوزها و آسیب دیدن مدار میشود. برای غلبه بر این مشکل، میتوان از مقاومت پولآپ بین ورودی و منبع تغذیه استفاده کرد. نحوه انجام این کار در شکل زیر نشان داده شده است.

با استفاده از این دو مقاومت پولآپ (یک مقاومت به ازای هر ورودی)، زمانی که کلیدهای a و b باز باشند، ورودی به صورت موثری به منبع تغذیه متصل میشود. چون جریان ورودی به گیتهای منطقی مقدار بسیار کوچکی است، مقدار افت ولتاژ در مقاومتهای پولآپ بسیار ناچیز بوده و در نتیجه تقریبا ولتاژ ۵ ولت در منبع تغذیه به صورت کامل به پینهای ورودی میرسد و وضعیت را به حالت یک منطقی تغییر میدهد. اگر کلیدهای a و b بسته باشند، ورودی به ولتاژ صفر ولت زمین متصل میشود و مانند حالت قبل سبب ایجاد سطح صفر منطقی در ورودی میشود. اما در این حالت مدار اتصال کوتاه به وجود نمیآید؛ زیرا مقاومتهای پولآپ باعث میشوند که جریان بسیار کوچکی مطابق با قانون اهم از طریق کلید به زمین عبور کند.

با استفاده از یک مقاومت پولآپ مانند روش بالا، ورودی همیشه، بسته به وضعیت کلید، یک حالت منطقی قطعی دارد، یا سطح منطقی یک و یا سطح منطقی صفر. در نتیجه خروجی خروجی گیت یعنی Q، دارای عملکرد مناسب خواهد بود. با جلوگیری از ورودی خود-بایاس و شناور میتوان شرایط کلیدزنی را دقیقا تنظیم کرد. حال این سوال پیش میآید که اگر استفاده از مقاومت پولآپ برای جلوگیری از اتصال کوتاه و نیز داشتن خروجی دلخواه ضروری است، مقدار این مقاومت باید چگونه تعیین شود؟

محاسبه مقدار مقاومت پول آپ

تمام گیتهای منطقی دیجیتال، آیسیها و میکروکنترلرها نهتنها در ولتاژ کاری خود، بلکه در جریان جذبشده (Current Sinking) و توانایی هر پین ورودی در تامین (Sourcing) جریان درای محدودیت هستند. مدارات منطقی دیجیتال، با استفاده از دو حالت باینری عمل میکنند که معمولا توسط دو سطح ولتاژ نشان داده میشوند: ولتاژ بالا یا $$V_H$$ برای سطح منطقی یک و ولتاژ پایین یا $$V_L$$ برای سطح منطقی صفر.

اما غیر از این دو حالت منطقی، بازههایی از ولتاژهای مختلف وجود دارند که در این بازهها ولتاژهای بالاتر و پایینتر از دو سطح ولتاژ منطقی تعریف میشوند.

به عنوان مثال، برای گیتهای منطقی سری TTL 74LS xxxx، در شکل زیر سطح ولتاژ متناظر با سطح منطقی یک و صفر نشان داده شده است.

ولتاژ $$V_{IH(min)} = 2 V$$ مقدار کمینه ولتاژ ورودی است که به عنوان ورودی سطح یک منطقی شناسایی میشود. در مقابل، ولتاژ $$V_{IL(max)} = 0.8 V$$ مقدار بیشینه ولتاژی است که اگر در ورودی دریافت شود، به عنوان ولتاژ سطح صفر منطقی شناخته میشود. یه عبارت دیگر سیگنالهای ورودی این آیسیها، اگر در بازه ۰ تا ۰٫۸ ولت باشند، به عنوان سطح صفر منطقی و اگر در بازه ۲ تا ۵ ولت باشند، به عنوان سطح یک منطقی در نظر گرفته میشوند. توجه کنید که تمام ولتاژها بین ۰٫۸ تا ۲ ولت، نه به عنوان سطح منطقی صفر و نه به عنوان سطح یک در نظر گرفته نمیشوند.

زمانی که گیتهای منطقی به صورت متصل با یکدیگر مورد استفاده قرار میگیرند، جریان از خروجی یک گیت به ورودی گیت دیگر جریان مییابد. مقدار جریانی که در ورودی یک گیت پایه منطقی TTL مورد نیاز میباشد، بستگی به این دارد که آیا ورودی در سطح منطقی صفر قرار دارد و یا سطح یک. اگر ورودی در سطح صفر منطقی باشد، به عنوان منبع جریان (Current-Sourcing) عمل میکند و اگر ورودی در سطح یک منطقی باشد، به عنوان چاه جریان (Current-Sinking) در نظر گرفته میشود.

اگر ورودی گیت منطقی مقدار HIGH داشته باشد، جریانی به درون ورودی آیسی TTL جاری میشود؛ زیرا ورودی در واقع مانند یک مسیر برای جریان عمل میکند که مستقیما به زمین متصل شده است. این جریان ورودی که $$I_{IH(max)} $$ نام دارد، در واقع دارای علامت مثبت است؛ زیرا به درون گیت وارد میشود و برای اکثر آیسیهای TTL سری 74LSxxxx مقداری برابر با ۲۰ میکرو آمپر است.

از طرف دیگر، زمانی که ورودی گیت منطقی در حالت LOW قرار دارد، جریان به خارج از گیت منطقی جاری میشود؛ زیرا ورودی در واقع مانند مسیری است که مستقیما به منبع تغذیه متصل شده است. این جریان ورودی که $$I_{IL(max)}$$ نام دارد، این بار دارای علامت منفی است؛ زیرا از گیت خارج میشود و برای اکثر آیسیهای TTL سری 74LSxxxx مقداری برابر با ۴۰۰ میکرو آمپر است.

توجه کنید که مقدار ولتاژ و جریان سطوح منطقی LOW و HIGH در آیسیهای سریهای مختلف با یکدیگر متفاوت هستند و در آیسیهای منطقی خانواده CMOS مقدار بسیار کوچکتری دارند. همچنین مقدار جریان و ولتاژ ورودی برای میکروکنترلرها، PLC، آردوینو (Arduino) و رزبری پای (Raspberry Pie) با یکدیگر متفاوت هستند. بنابراین، باید به این مقادیر دقت شود و تمام آنها را قبل از استفاده، در دیتاشیت مربوطه مطالعه کرد.

حال با دانستن تمام این اطلاعات، میتوان مقدار مورد نیاز برای قرار دادن به عنوان یک مقاومت پولآپ را محاسبه کرد. فرمول زیر نشاندهنده نحوه محاسبه مقاومت پولآپ برای یک آیسی از خانواده 74LSxxxx را نشان میدهد.

$$R_{MAX}=\frac{V_{CC} - V_{IH(MIN)}}{I_{IH}} = \frac{5-2}{20 \times 10^{-6}} =150 K \Omega$$

بنابراین با استفاده از قانون اهم میتوان نشان داد که مقدار مقاومت لازم برای افت ولتاژ ۳ ولت در یک آیسی از این خانواده برابر با 150 کیلو اهم است. اگرچه این مقدار مقاومت به لحاظ تئوری درست است، اما هیچ جایی برای خطا باقی نمیگذارد؛ زیرا مقدار بیشینه افت ولتاژ در طول مقاومت را به ازای جریان ورودی بیشینه دارد.

در حالت ایدهآل، هدف این است که سطح یک منطقی تا حد امکان به ولتاژ منبع تغذیه ($$V_{CC}$$) نزدیک باشد، تا به صورت کامل تضمین شود که گیت از طریق مقاومت پولآپ میتواند سطح یک منطقی را دریافت کند. کاهش مقدار مقاومت پولآپ، حاشیه خطای بزرگتری را در اختیار مدار قرار میدهد. با این حال، باید به این نکته توجه شود که مقدار مقاومت پول آپ نباید به حدی کاهش یابد که اجازه دهد جریان بالایی به گیت منطقی وارد شود و اتلاف توان افزایش یابد.

حال اگر فرض کنیم که افت ولتاژ در طول مقاومت به اندازه ۱ ولت، منجر به دو برابر شدن ولتاژ ورودی به اندازه ۴ ولت شود، مقدار محاسبه شده برای تک مقاومت پول آپ بربر با ۵۰ کیلو اهم خواهد بود. با کاهش بیشتر مقدار مقاومت پول آپ، افت ولتاژ کمتری تولید میشود، اما جریان ورودی افزایش مییابد.

مثال ساده بالا، روش محاسبه مقدار بیشینه مقاومت پول آپ که برای بایاس یک گیت منطقی تکی لازم است را نشان میدهد. اما این امکان وجود دارد که به روش مشابه از مقاومت پول آپ برای بایاس چند ورودی در سطح منطقی یک استفاده کرد. به عنوان مثال، فرض کنید که در یک مدار دیجیتال طراحی شده، ده پین ورودی از گیتهای منطقی بدون استفاده باقی ماندهاند. همانطور که یک گیت منطقی 74LS جریان $$I_{IH(MAX)}$$ به اندازه ۲۰ میکرو آمپر دارد، ده گیت منطقی به جریان کلی برابر با $$10 \times 20 \mu A = 200 \mu A$$ نیاز دارند. بنابراین مقدار بیشینه مقاومت پین آپ مورد نیاز برای تغذیه ده ورودی استفاده نشده، به صورت زیر محاسبه میشود.

$$R_{MAX}=\frac{V_{CC} - V_{IH(MIN)}}{10 \times I_{IH}} = \frac{5-2}{10 \times 20 \times 10^{-6}} =15 K \Omega$$

در این مثال تعداد ورودیهای استفاده نشده ۱۰ عدد بودند، اما اگر تعداد n ورودی TTL به یکدیگر متصل شوند، جریانی که از مقاومت پول آپ میگذرد برابر با $$n \times I_{IH(MAX)}$$ است. در این حالت نیز مقدار محاسبه شده برای مقاومت، مقداری دقیقی است و هیچ فضایی برای خطا باقی نمیگذارد. بنابراین با کاهش افت ولتاژ به اندازه یک ولت (و یا هر مقدار دلخواه دیگر)، به مقدار مقاومت ۵ کیلو اهم برای مقاومت پول اپ میرسیم.

مثال 1

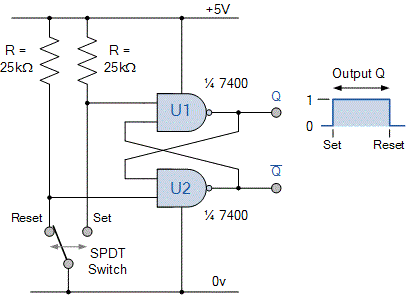

دو گیت NAND از نوع TTL 74LS00 برای تشکیل یک مدار فلیپ فلاپ ست-ریست بایاستابل ساده همراه با یک کلید تک پل دو زبانه (Single-Pole Double-Throw) مانند شکل زیر به یکدیگر متصل شدهاند.

مقدار بیشینه مقامت پول آپ را برای شرایطی محاسبه کنید که ولتاژ ورودی نشاندهنده سطح یک منطقی با باز بودن کلید، برابر با ۴٫۵ ولت باشد. همچنین مقدار جریانی که از مقاومت در زمان بسته بودن کلید میگذرد را نیز محاسبه کنید. اطلاعات زیر در دیتاشیت گیت منطقی داده شده است:

$$V_{CC}= 5V\\

V_{IH} = 4.5 V\\

I_{IH(MAX)} = 20 \mu A$$

راهحل

برای محاسبه مقاومت پول آپ به صورت زیر عمل میکنیم:

$$R_{MAX}=\frac{V_{CC} - V_{IH}}{I_{IH}} = \frac{5-4.5}{20 \times 10^{-6}} =25 K \Omega$$

جریان عبوری از طریق مقاومت پول آپ نیز به صورت زیر محاسبه میشود:

$$I_{R}=\frac{V_{CC}}{R} = \frac{5V}{25 K \Omega} =200 \mu A$$

مقاومت پول داون

مقاومت پول داون یا پایینکش (Pull-Down) نیز به طریق مشابه با مقاومت پول آپ کار میکند که در قسمت قبل به توضیح آن پرداختیم. اما تفاوت بزرگ در این است که این بار ورودی گیت منطقی به زمین یا ولتاژ صفر متصل میشود و در سطح منطقی LOW قرار میگیرد و ممکن است توسط عملکرد یک کلید مکانیکی به سطح منطقی یک باز گردد. این پیکربندی مقاومت پول داون، مخصوصا برای مدارت دیجیتالی مانند لچها، فلیپ فلاپها و یا شمارندهها مناسب و مفید است؛ زیرا در این قطعات برای تغییر حالت، به یک تریگر تک ضربهای مثبت، هنگام بسته شدن آنی کلید نیاز داریم. با اینکه عملکرد مقاومت پول داون بسیار شبیه به مقاومت پول اپ است، اما مقدار مقاومت غیرفعال (Passive) پول داون در گیتهای منطقی TTL نسبت به گیتهای مشابه اما از نوع CMOS بسیار ضروریتر است. زیرا گیتهای منطقی TTL جریان بسیار بیشتری را از منبع در حالت LOW منطقی جذب میکنند.

همانطور که در بالا مطرح شد، مقدار بیشینه سطح ولتاژ نشاندهنده سطح صفر منطقی در یک گیت 74LSxxx در بازهای بین 0 تا 0٫۸ ولت میباشد. همچنین در سطح LOW منطقی، مقدار جریان جذب منبع به ۴۰۰ میکرو آمپر میرسد. بنابراین برای محاسبه مقدار مقاومت پول داون به صورت زیر عمل میکنیم:

$$R_{MAX}=\frac{V_{IL(MAX)} - 0 }{I_{IL}} = \frac{0.8 -0}{400 \times 10^{-6}} =2 K \Omega$$

بنابراین مقدار بیشینه مقاومت پول داون 20 کیلو اهم به دست میآید. این مقدار مقاومت پول داون هیچ امکان خطایی را در مدار در نظر نگرفته است و مقدار افت ولتاژ بیشینه مقدار ممکن است. بنابراین اگر مقاومت بسیار بزرگ باشد، افت ولتاژ در طول مقاومت پول داون ممکن است منجر به این شود که ولتاژ ورودی گیت، فراتر از بازه نرمال ولتاژ LOW شود. بنابراین برای اطمینان از کلیدزنی صحیح، بهتر است ولتاژ ورودی را ۰٫۵ ولت و یا کمتر در نظر بگیریم. اگر افت ولتاژ در طول مقاومت را برابر با ۰٫۴ ولت در نظر بگیریم، با جایگذاری در فرمول بالا به مقدار ۱ کیلو اهم به عنوان مقاومت پول داون میرسیم. با کاهش بیشتر مقدار مقاومت پول داون، در واقع افت ولتاژ کوچکتری را در اتصال ورودی به زمین تولید میکنیم. مقدار ۴۰۰ میکرو آمپر نوشته شده در دیتاشیت گیت منطقی کمینه مقدار جریان سطح LOW را نشان میدهد اما امکان دارد که جریان از این مقدار بیشتر نیز باشد.

اتصال تعداد بیشتری ورودی به یکدیگر باعث افزایش جریان عبوری از مقاومت میشود. اگر مطابق مثالهی قبل تعداد ده ورودی را به یکدیگر متصل کنیم، جریان گذرا از مقاومت پول داون برابر با ۱۰۰ اهم، برابر با ۴ میکرو آمپر خواهد شد.

ممکن است این سوال پیش بیاید که دلیل استفاده از مقاومت پول داون چیست؟ چرا با اتصال مستقیم ورودی به زمین مقدار آن را به سطح صفر منطقی تغییر نمیدهیم؟ قطعا اتصال مستقیم ورودی بدون استفاده از مقاومت پول داون منجر به تغییر ورودی به سطح صفر منطقی میشود، اما چون ورودی گیت به صورت دائمی به زمین متصل شده است، استفاده از مقاومت پول داون باعث میشود که جریان خروجی از پین ورودی گیت محدود شود و در نتیجه توان تلفشده نیز کاهش یابد، در حالیکه گیت سطح منطقی LOW را نیز حفظ کرده است.

خروجی کلکتور باز

تا این قسمت با نحوه استفاده از مقاومتهای پول داون و پول آپ در گیتهای منطقی به منظور کنترل سطح ولتاژ آشنا شدیم. اما میتوان از مقاومت پول آپ در خروجی گیتها نیز برای اتصال گیتها با تکولوژیهای مختلف مانند اتصال گیت TTL به گیت CMOS استفاده کرد. کاربرد دیگر این مقاومتها در خطوط انتقال است که ولتاژها و جریانهای بالا نیاز است.

به منظور استفاده از مقاومتهای پول داون و پول آپ برای اهداف بالا، بعضی از گیتهای منطقی به نحوی تولید میشوند که خروجی داخلی گیت، کلکتور باز (Open-Collector) از چپ (Left Open) هستند، به این معنی که گیت منطقی در واقع خروجی را به سطح HIGH نمیبرد، بلکه فقط به سطح LOW میآورد، زیرا این کار وظیفه مقاومت پول آپ خارجی است. به عنوان مثالی از چنین گیتهایی، میتوان به TTL 74LS01 اشاره کرد که یک گیت NAND با دو ورودی دوتایی است که بر خلاف آیسی استاندارد TTL 74LS00 دارای خروجی کلکتور باز است.

خروجیهای کلکتور باز و یا در مورد آیسیهای تکنولوژی CMOS خروجیهای درین باز (Open-Drain)، معمولا در آیسیهای درایور، اینورتر و بافر مورد استفاده قرار میگیرند. این خروجیها، جریان و یا ولتاژهای خروجی بسیار بزرگتر را نسبت به آنچه با استفاده از گیتهای منطقی معمولی به دست میآیند، ممکن میسازند. مثلا برای راهاندازی یک بار بزرگ مانند نمایشگر LED، رله و یا یک موتور جریان مستقیم از این نوع گیتهای منطقی استفاده میشود.

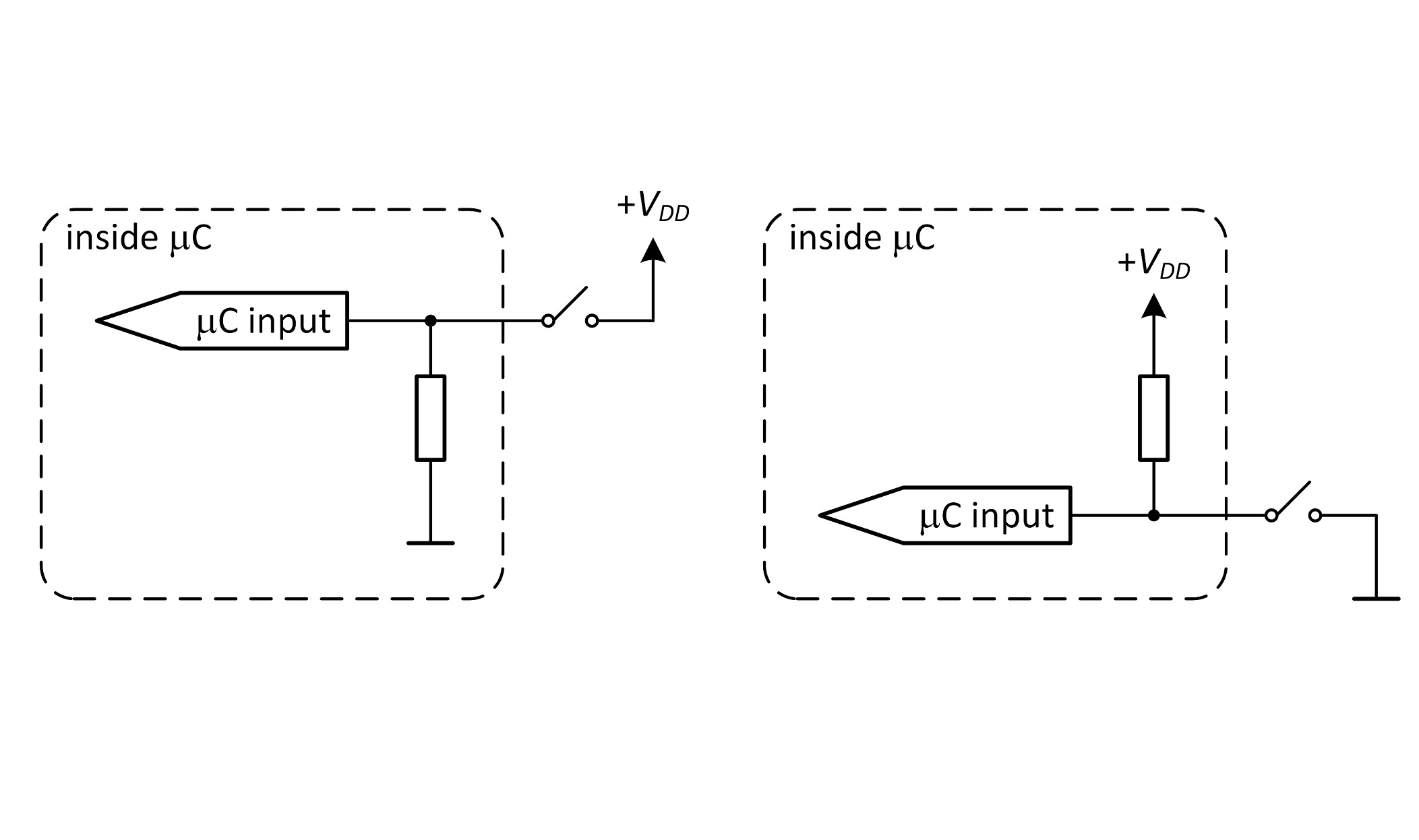

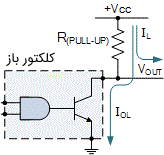

گیتهای منطقی، میکروکنترلرها و سایر مدارهای منطقی که دارای خروجی کلکتور باز هستند، قادر نیستند خروجی خود را به حالت HIGH ببرند؛ زیرا مسیر داخلی برای ولتاژ منبع تغذیه وجود ندارد. وجود این شرایط به این معنی است که خروجی آنها یا در حالت LOW به زمین متصل است و یا در حالت HIGH شناور است. بنابراین یک مقاومت پول آپ خارجی ($$R_{PULL-UP}$$) برای اتصال از ترمینال کلکتور باز متعلق به ترانزیستور به منبع تغذیه $$V_{CC}$$ لازم است. نمونهای از یک خروجی کلکتور باز در تصویر زیر نشان داده شده است.

با استفاده از یک مقاومت پول آپ خارجی، خروجی به طریق مشابه با یک گیت منطقی در شرایط نرمال کار میکند، که در این حالت، زمانی که ترانزیستور خروجی باز یا خاموش باشد، خروجی در سطح HIGH منطقی قرار دارد و زمانی که ترانزیستور در حالت روشن یا متصل باشد، خروجی در سطح LOW قرار دارد. بنابراین ترانزیستور برای تغییر سطح خروجی به صفر منطقی روشن میشود.

اندازه مقاومت پول آپ خروجی به مقدار بار متصل شده و نیز افت ولتاژ در طول مقاومت هنگام خاموش بودن ترانزیستور بستگی دارد. زمانی که خروجی در حالت LOW قرار دارد، ترانزیستور باید قادر باشد که جریان بار را از طریق مقاومت پول آپ جذب (Sink) کند. به طریق مشابه زمانی که ترانزیستور خاموش باشد و خروجی در سطح منطقی HIGH قرار داشته باشد، جریان عبوری از مقاومت پول آپ باید به اندازه کافی برای هر وسیله متصل به آن بزرگ باشد.

مشابه با آنچه قبلا در مورد ورودیها مشاهده کردیم، خروجیهای یک گیت منطقی نیز تحت دو سطح منطقی عمل میکنند که این دو سطح، توسط دو ولتاژ متفاوت نشان داده میشوند. یکی از این ولتاژها، ولتاژ بالا یا $$V_H$$ برای سطح یک منطقی و دیگری ولتاژ پایین یا $$V_L$$ برای سطح منطقی صفر است. با توجه به این دو سطح ولتاژ، بازههای ولتاژی متفاوتی وجود دارند، که عملکرد مدار با توجه به آنها تعیین میشود.

$$V_{OH(min)}$$ کمینه ولتاژ خروجی است که به عنوان ولتاژ خروجی سطح HIGH شناخته میشود و این مقدار برای گیتهای TTL برابر با ۲٫۷ است. $$V_{OL(max)}$$ نیز بیشینه ولتاژ خروجی است که به عنوان خروجی سطح صفر منطقی شناسایی میشود. این مقدار در گیتهای TTL برابر با ۰٫۵ است. بنابراین میتوان نتیجه گرفت که در مورد آیسی TTL 74LSxxx ولتاژهای خروجی بین ۰ تا ۰٫۵ به عنوان ولتاژ سطح LOW و ولتاژهای خروجی بین ۲٫۷ تا ۵ به عنوان ولتاژ سطح HIGH در نظر گرفته میشوند.

مقادیر زیر برای یک آیسی 7401 کلکتور باز مربوط به گیت NAND هستند:

$$V-{CC}= 5 V\\V_{OL}=0.5 V\\I_{OL(max)} =8mA$$

هنگام استفاده از گیتهای منطقی کلکتور باز، مقدار مقاومت پول آپ مورد نیاز با استفاده از فرمول زیر تعیین میشود:

$$R_{min} = \frac{V_{CC} - V_{OL (max)}}{I_{OL}}= \frac{5-0.5}{8\times 10^{-3}}= 562 \Omega$$

توجه کنید که مقدار مقاومت پول آپ باید به نحوی محاسبه شود که جریان عبوری از آن از مقدار $$I_{OL(max)}$$ بیشتر نشود.

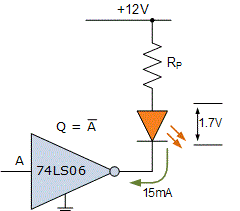

همانطور که قبلا نیز اشاره شد، گیتهای منطقی کلکتور باز برای درایو بارهایی که به سطوح ولتاژ و جریان بالا نیاز دارند، مناسب هستند. TTL 74LS06 که یک آیسی متعلق به درایور بافر اینورتر است، دارای $$I_{OL(max)}$$ در حدود ۴۰ میلی آمپر است و نیز $$V_{OH(max)}$$ آن برخلاف آیسیهای متداول که ۵ ولت است، در سطح ۳۰ ولت قرار دارد. اما خود آیسی باید از ولتاژ تغذیه ۵ ولت استفاده کند. بنابراین 74LS06 به ما اجازه اتصال بارهای تا ۴۰ میلی آمپر را میدهد.

مثال 2

از آیسی 74LS06 برای کنترل یک LED، که با ولتاژ ۱۲ ولت تغذیه میشود، مانند شکل زیر استفاده میکنیم. جریان مورد نیاز LED در افت ولتاژ ۱٫۷ ولت برابر با ۱۵ میلی آمپر است. همچنین مقدار $$V_{OL}$$ آیسی هنگام روشن بودن ۰٫۱ ولت است. مقدار مقاومت پول آپ مورد نیاز در این آیسی را محاسبه کنید.

راهحل

میتوان درایورهای کلکتور باز را همانند درایور رلههای الکترومکانیکی کوچک، لامپها و موتورهای DC به کار بست. این ادوات معمولا برای عملکرد صحیح، به ولتاژ ۵ یا ۱۲ ولت یا بیشتر در جریان ۱۰ تا ۲۰ میلی آمپر نیاز دارند. دو یا تعداد بیشتری از گیتهای TTL کلکتور باز میتوانند مستقیما به یکدیگر وصل شوند و از یک مقاومت پول آپ خارجی استفاده کنند. در نتیجه خروجیها به صورت موثری با یکدیگر AND میشوند و عملکرد مشابه با زمانی خواهد بود که آیسی به یک گیت AND متصل شده باشد.

$$R_{P} = \frac{V}{I} = \frac{V_{CC} - V_{LED} - V_{OL}}{I_{LED}}$$

$$R_{P} = \frac{12 -1.7 - 0.1}{15 \times 10^ {-3}}$$

اگر مطالب بیان شده برای شما مفید بوده و میخواهید درباره موضوعات مرتبط با آن بیشتر بدانید، پیشنهاد میکنیم به آموزشهای زیر مراجعه کنید:

- مجموعه آموزشهای مهندسی برق

- آموزش مدارهای الکتریکی ۱

- مجموعه آموزشهای مهندسی الکترونیک

- آموزش مدارهای الکتریکی ۱ (مرور و حل تست)

- قضیه هم پاسخی — به زبان ساده

- قضیه نورتن (Nortons Theorem) — مفاهیم اصلی

- قضیه تونن (Thevenin’s Theorem) — مفاهیم کلیدی

^^

سلام خسته نباشین وقتی تو میکروکنترلر یه پایه ورودی رو پول آپ مییکنیم برای گرفتن ورودی میتونیم با یه دکمه پایه پول آپ شده رو مستقیم به زمین بزنیم یا میکرو آسیب میبینه ممنون میشم اگه سریع جواب بدین

سلام

در قسمت “کلکتور باز” مقاله بند شیش، غلط املایی داره

زامانی->زمانی

سلام.

اصلاحات لازم انجام شد.

از همراهی و بازخورد شما سپاسگزاریم.

خانم مهندس سلام من دیتا شیت برد اردوینو نانو رو دانلود کردم میخواستم مقاومت پول اپ و پول داون مناسب براش رو محاسبه کنم و همچنین میزان جریانی که برای ورودی و خروجی های برد مناسبه رو ببینم هیچ کدوم داخل دیتاشیت نیست میشه راهنمایی کنید

ممنون