فلیپ فلاپ JK – از صفر تا صد (+ دانلود فیلم آموزش رایگان)

فلیپ فلاپ JK یکی از رایجترین و پرکاربردترین فلیپ فلاپها در طراحیهای منطقی است. مدارهای دیجیتال مبتنی بر فلیپ فلاپ ست-ریست (Set-Reset Flip-Flops) مزایا و کاربردهای بسیاری در طراحی مدارات منطقی ترتیبی دارند.

اما این فلیپ فلاپها دو مشکل اساسی دارند:

- شرایط Set=0 و Reset=0 یعنی (S=R=0) هیچ وقت نباید اتفاق بیفتد، زیرا منجر به حالت ناپایدار و غیرقابل پیشبینی میشود.

- در زمانی که ورودی فعالساز (Enable) در حالت یک منطقی قرار دارد، اگر Set یا Reset تغییر سطح منطقی دهند، این احتمال وجود دارد که عمل نگهداری یا (Latching) اتفاق نیفتد.

برای غلبه بر این دو مشکل اساسی در طراحی فلیپفلاپهای SR، فلیپفلاپهای JK توسعه یافتهاند. این فلیپفلاپ محبوبترین فلیپفلاپ مورد استفاده است و به عنوان یک مدار فلیپفلاپ عمومی شناخته میشود. منظور از فلیپفلاپ عمومی این است که از این فلیپفلاپ به عنوان مبنای طراحی مدارات دیجیتال استفاده میشود. در این مطلب ابتدا ساختمان و نحوه کار فلیپ فلاپ JK را بررسی کرده و سپس به بیان مشکل اصلی این نوع فلیپ فلاپ پرداخته و راه حل رفع مشکل را بررسی میکنیم.

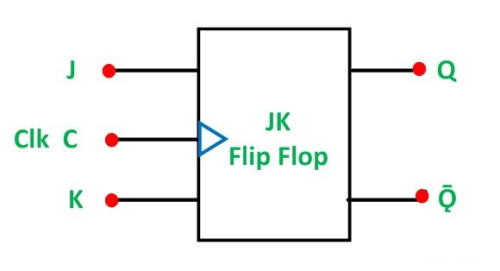

در شکل زیر نماد فلیپ فلاپ JK نشان داده شده است. علامت مثلث در کنار ورودی پالس ساعت (CLK) بدین معنی است که فلیپفلاپ فقط در لبههای سیگنال ساعت عمل میکند. بسته به نوع آیسی، فلیپفلاپ ممکن است حساس به لبه بالارونده یا پایینرونده باشد. دقت کنید که برخلاف فلیپفلاپ SR که در آن حروف S و R به ترتیب شکل مختصر شده Set و Reset هستند، در فلیپفلاپ JK حروف J و K شکل اختصاری هیچ کلمهای نیستند و توسط مخترع این فلیپفلاپ یعنی جک کیبلی (Jack Kilby) انتخاب شدهاند.

عملکرد فلیپ فلاپ JK مشابه با فلیپفلاپ SR است، با این تفاوت که در فلیپفلاپ JK حالت ممنوعه وجود ندارد و ورودیهای J و K به صورت همزمان میتوانند یک (1) منطقی شوند. اساسا فلیپ فلاپ JK یک فلیپفلاپ SR به علاوه یک مدار پالس ساعت است که از وضعیت ممنوعه که در فلیپفلاپ SR وجود داشت، جلوگیری میکند. به عبارت دیگر مدار اضافهشده طوری عمل میکند که ورودیهای فلیپفلاپ SR هیچوقت به صورت همزمان یک منطقی نشوند. به همین دلیل چهار حالت محتمل برای ورودی فلیپفلاپ JK وجود دارد: سطح یک منطقی، سطح صفر منطقی، عدم تغییر وضعیت و حالت (Toggle). سه حالت اول مشابه فلیپفلاپ SR است.

حالت چهارم بدین معنا است که با اعمال هر پالس ساعت به فلیپفلاپ، وضعیت خروجی قرینه میشود. اگر خروجی فلیپفلاپ در ابتدا یک منطقی باشد، با آمدن پالس ساعت اول، خروجی صفر منطقی و با آمدن پالس ساعت دوم خروجی صفر منطقی میشود. به همین ترتیب با آمدن هر پالس ساعت جدید تغییر وضعیت از صفر به یک و یا از یک به صفر منطقی اتفاق میافتد.

ساختمان فلیپ فلاپ JK

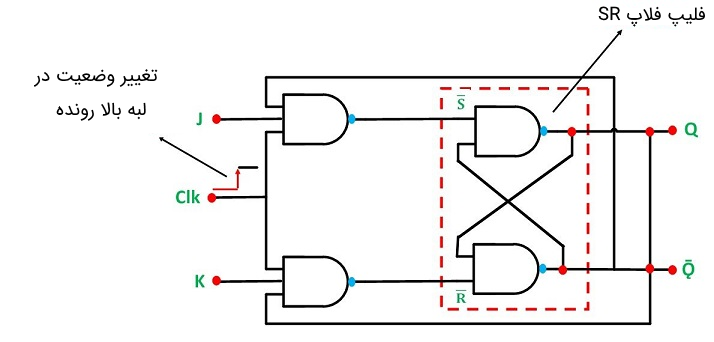

هر دو ورودی S و R در مولتیویبراتور دوحالته SR (همان فلیپفلاپ SR) با ورودیهای جدید J و K جایگزین شدهاند. بنابراین روابط J=S و K=R برقرار است. گیتهای AND دو-ورودی در مدار فلیپفلاپ SR نیز با گیتهای NAND سه-ورودی جایگزین شده است که ورودی سوم آنها به ترتیب به خروجیهای و فلیپفلاپ SR متصل میشوند.

این کوپل متقابل (Cross Coupling) فلیپفلاپ SR، باعث میشود که حالت نامعتبر موجود در فلیپفلاپ SR، یعنی S=1 و R=1 به عنوان وضعیت جدید Toggle مورد استفاده قرار گیرد.

اگر مدار در شرایط Set قرار بگیرد، آنگاه ورودی J فلیپفلاپ توسط خروجی گیت NAND پایینی بیاثر میشود، زیرا این خروجی صفر منطقی خواهد شد. در گیت NAND نیز اگر یکی از ورودی ها صفر منطقی شود، خروجی آن گیت صرفنظر از سایر ورودیها همواره در وضعیت یک منطقی میماند. به طور مشابه، اگر مدار در شرایط Reset قرار بگیرد، آنگاه ورودی K فلیپفلاپ توسط خروجی گیت NAND بالایی که صفر منطقی است، بیاثر میشود. بنابراین چون خروجیهای و همواره در وضعیت منطقی قرینه هم هستند، از آنها میتوان برای کنترل کردن فلیپفلاپ استفاده کرد. زمانی که هر دو ورودی J و K به صورت همزمان یک منطقی شوند، فلیپفلاپ در وضعیت Toggle قرار میگیرد.

| وضعیت | Q | K | J | |

| عدم تغییر حافظه | 0 | 0 | 0 | 0 |

| Reset کردن Q به صفر | 0 | 1 | 1 | 0 |

| Set کردن Q به مقدار یک | 1 | 0 | 0 | 1 |

| تنظیم مجدد | 1 | 0 | 1 | 1 |

مد Toggle در فلیپ فلاپ JK

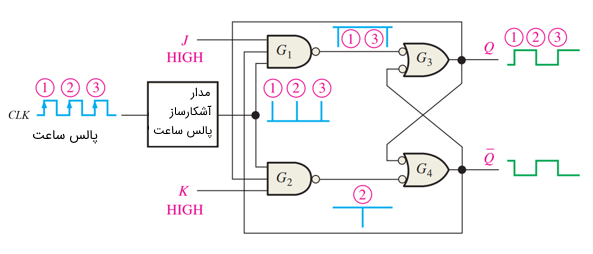

عملکرد Toggle در ادامه به صورت واضحتری نشان داده شده است. ورودیهای J و K هر دو یکِ منطقی شدهاند و فرض میشود در ابتدا خروجی Q فلیپفلاپ در وضعیت صفر منطقی قرار داشته باشد. بلوک آشکارسازی پالس ساعت برای تشخیص لبههای بالارونده سیگنال ساعت ورودی استفاده میشود. به صورتی که در زمان ایجاد لبه بالارونده در سیگنال ساعت یک پالس خیلی کوتاه در خروجی آن ایجاد میشود که همین پالس خیلی کوتاه برای تغییر وضعیت فلیپفلاپ کافی است. پس زمانهای 1، 2 و 3 در خروجی این بلوک متناظر با لبههای بالارونده 1، 2 و 3 در سیگنال ساعت در ورودی آن است.

تغییر وضعیت فلیپ فلاپ بعد از اعمال لبه اول

حال گیت NAND اول (G1) را در زمانهای قبل از اعمال پالس ساعت 1 در نظر بگیرید. خروجی فلیپفلاپ صفر منطقی و خروجی آن یک منطقی و همینطور خروجی مدار آشکارساز نیز صفر منطقی است. بنابراین خروجی گیت G1 یک منطقی خواهد شد که آن هم باعث میشود هر دو ورودی گیت G3 یک منطقی شوند. بنابراین، خروجی گیت G3 صفر منطقی میشود. پس مدار در وضعیت Reset قفل شده است. حال فرض کنید که پالس کوتاه اول در خروجی بلوک آشکارساز به گیت G1 اعمال شود. در آن لحظه هر سه ورودی گیت G1 یک منطقی میشوند. بنابراین خروجی آن صفر منطقی خواهد شد.

حال چون خروجی گیت G1 ورودی گیت G3 است و ورودی اول G3 صفر منطقی شده است، صرفنظر از ورودی دیگر آن، خروجی این گیت یک منطقی خواهد شد. این امر به نوبه خود باعث میشود که تمام ورودیهای گیت G4 یک منطقی شوند که این هم در نهایت منجر به صفر شدن خروجی این گیت صفر منطقی خواهد شد. بنابراین وضعیت جدید مدار و میشود.

تغییر وضعیت فلیپ فلاپ بعد از اعمال لبه دوم

حال مدار را در حالتی که لبه بالارونده دوم به مدار اعمال میشود، بررسی میکنیم. به گیت G2 قبل از اعمال لبه دقت کنید. ورودی اول آن صفر منطقی است که باعث میشود خروجی این گیت صرفنظر از وضعیت منطقی سایر ورودیها یک منطقی شود. اکنون به گیت G4 توجه کنید که هر دو ورودی آن یک منطقی است. بنابراین خروجی این گیت که همان است، صفر منطقی خواهد شد. بنابراین مدار در وضعیت Set قفل شده است.

حال زمانی که لبه بالارونده دوم به مدار اعمال میشود، ورودی اول گیت G2 یک منطقی خواهد شد که با توجه به این که سایر ورودیهای آن هم یک منطقی است، خروجی صفر منطقی شده و این باعث میشود که ورودی دوم گیت G4 صفر منطقی شود. این تغییر منجر به یکِ منطقی شدن خروجی آن میشود. پس خواهد شد. این تغییر هم باعث میشود که هر دو ورودی گیت G3 یک منطقی شوند. پس خروجی گیت G3 نیز به حالت Reset تغییر وضعیت پیدا میکند. بنابراین وضعیت جدید مدار به صورت و خواهد بود. این وضعیت مشابه وضعیت مدار قبل از اعمال لبه بالارونده اول بود. حال اگر لبههای جدید به مدار اعمال شود، تغییر وضعیت دوباره ایجاد خواهد شد.

در کل دقت کنید زمانی که فلیپفلاپ در وضعیت Reset قرار دارد، اعمال لبه به گیت G1 باعث تغییر وضعیت میشود. در طرف مقابل زمانی که فلیپفلاپ در وضعیت Set قرار دارد، اعمال لبه به گیت G2 باعث تغییر وضعیت خواهد شد.

مدهای کاری مشابه فلیپ فلاپ SR و JK

سایر مدهای کاری فلیپفلاپ JK دقیقا مشابه فلیپفلاپ SR است. برای مثال اگر فرض شود فلیپفلاپ در ابتدا در وضعیت Reset قرار داشته باشد و ورودی J = 1 و K = 0 به آن اعمال شود، مطابق شکل بالا، قبل از اعمال لبه ورودیهای اول و دوم یک منطقی و ورودی سوم صفر منطقی است. پس خروجی گیت G1 و به همین ترتیب گیت G3 صفر میشود.

اما اگر لبه به مدار اعمال شود، در لحظه اعمال آن هر سه ورودی گیت G1 یک منطقی میشود، پس خروجی آن صفر منطقی و در نهایت خروجی گیت G3 یک منطقی خواهد شد. در گیت G2 چون ورودی K همواره صفر منطقی است، تغییر وضعیت خروجی تاثیری روی آن ندارد و خروجی آن همواره برابر یک منطقی است. اما ورودی اول گیت G4 به دلیل خروجی یک منطقی خواهد شد. پس خروجی صفر منطقی میشود و تا زمانی که سیگنالهای منطقی جدیدی به ورودی فلیپفلاپ اعمال نشود، مدار در همین وضعیت باقی میماند.

مشکل اساسی فلیپ فلاپ JK

اگرچه مدار فلیپ فلاپ JK یک حالت بهبودیافته فلیپ فلاپ SR است، اما یک مشکل اساسی زمانبندی به نام «Race» دارد. فرض کنید فلیپفلاپ در وضعیت Toggle قرار داشته باشد، یعنی J = 1 و K = 1. همچنین فرض کنید که سیگنال پالس ساعت در سطح یک منطقی باشد. از نظر تئوری چون لبهای اتفاق نیفتاده است، پس تغییر وضعیتی هم در خروجی فلیپفلاپ نباید ایجاد شود. اما در فلیپفلاپهای واقعی به دلیل تفاوت تاخیر انتشار در گیتهای G1 تا G4، بعد از گذشت مدت زمان طولانی تغییر وضعیت ناخواسته در خروجی فلیپفلاپ ایجاد میشود یا به عبارت دیگر فلیپفلاپ ناپایدار و غیرقابل پیشبینی خواهد شد.

برای جلوگیری از این مشکل، تناوب پالس ساعت باید تا حد امکان کوچک باشد (فرکانس پالس ساعت بالا باشد). چون این عمل گاهی با آیسیهای ساخته شده با تکنولوژی TTL مقدور نیست، فلیپفلاپهای پیشرفتهتر یعنی «Master-Slave JK Flip-flop» توسعه یافتهاند.

فلیپفلاپ Master-Slave JK

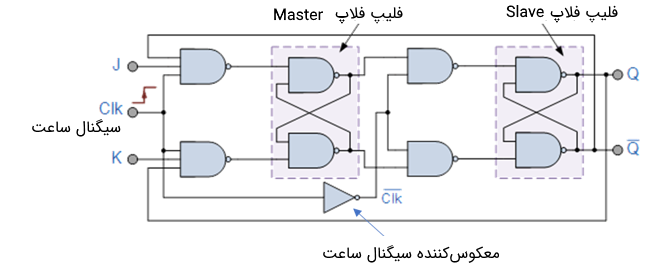

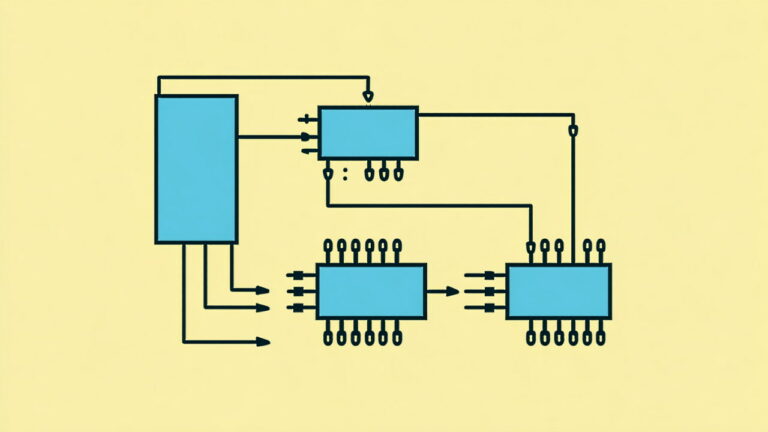

فلیپفلاپ Master-Slave JK با استفاده از دو فلیپفلاپ SR که به صورت پشت سر هم (سری) متصل شده است، مشکل زمانبندی فلیپفلاپهای JK معمولی را برطرف میکند. فلیپفلاپ اول به عنوان Master یا فرمانده عمل میکند و حساس به لبههای بالارونده سیگنال ساعت است. اما فلیپفلاپ دوم به عنوان Slave یا فرمانبر عمل کرده و حساس به لبههای پایینرونده سیگنال ساعت است. این امر باعث میشود فلیپفلاپ Master-Slave JK در دو مرحله تغییر وضعیت پیدا کند که هر مرحله آن وابسته به نیمسیکلهای متفاوت سیگنال ساعت هستند. شکل زیر بلوک دیاگرام فلیپفلاپ Master-Slave JK را نشان میدهد.

مطابق شکل بالا خروجیهای فلیپفلاپ Master به عنوان ورودیهای فلیپفلاپ Slave استفاده میشوند. همچنین خروجیهای فلیپفلاپ Slave نیز به ورودی فلیپفلاپ Master فیدبک شده است. برای اینکه دو فلیپفلاپ در دو لبه مختلف سیگنال ساعت عمل کنند، از یک گیت NOT به عنوان معکوسکننده سیگنال ساعت استفاده میشود. این بلوک باعث میشود که فلیپفلاپ Slave وابسته به لبه پایینرونده سیگنال ساعت شود در حالی که فلیپفلاپ Master وابسته به لبه بالارونده آن است. در ادامه به این مطلب میپردازیم که این مدار چگونه میتواند مشکل Race در فلیپفلاپهای JK معمولی را رفع کند.

اصول کاری فلیپ فلاپ Master-Slave JK

به منظور درک بهتر، دقت کنید که بلوک آشکارساز پالس در مدار وجود ندارد و در واقع مدار حساس به سطح است. پس فلیپفلاپ Mater حساس به سطح یک منطقی و فلیپفلاپ Salve حساس به سطح صفر منطقی است. پس تغییر وضعیت فلیپفلاپ Maser بر اساس ورودی JK زمانی اتفاق میافتد که سیگنال ساعت در سطح یک منطقی باشد و همچنین تغییر وضعیت فلیپفلاپ Slave بر اساس ورودی JK زمانی اتفاق میافتد که سیگنال ساعت در سطح صفر منطقی باشد.

مشکل Race زمانی رخ میداد که هر سه ورودی J ،K و سیگنال ساعت یک منطقی باشند. اگر این اتفاق بیفتد، خروجی فلیپفلاپ Maser تغییر وضعیت پیدا میکند اما به دلیل اینکه خروجی گیت معکوسکننده صفر منطقی میشود، گیتهای فلیپفلاپ Slave فعال نمیشوند و در نتیجه خروجی فلیپفلاپ Master-Slave JK بدون تغییر باقی میماند. برای اینکه تغییر حالت در وضعیت خروجی فلیپفلاپ Master-Slave JK پیش بیاید، باید خروجی گیت معکوسکننده یک منطقی شود و این امر زمانی اتفاق میافتد که سیگنال ساعت از سطح یک منطقی به سطح صفر منطقی برود.

بنابراین میتوان نتیجه گرفت که تغییر وضعیت خروجی فلیپفلاپ Master-Slave JK تنها زمانی ایجاد میشود که لبه پایینرونده در سیگنال ساعت ایجاد شود و زمانی که سیگنال ساعت ثابت و در وضعیت یک منطقی است، هیچ تغییری در خروجی آن ایجاد نمیشود.

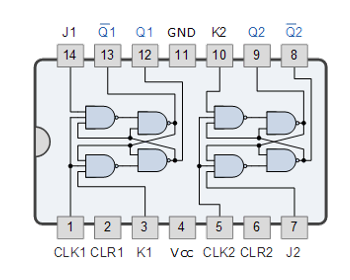

آیسی TTL 74LS73 حاوی دو فلیپفلاپ JK معمولی است که به دو صورت میتوان از آن استفاده کرد. در حالت اول، این آیسی به عنوان دو فلیپفلاپ JK معمولی استفاده میشود و در حالت دوم با اتصال سری آنها به عنوان فلیپفلاپ Master-Slave JK به کار میرود. بلوک دیاگرام این آیسی در شکل زیر نشان داده شده است. مطابق این شکل پایههای 3، 14، 1 و 12 به ترتیب ورودیهای K ،J، سیگنال ساعت و خروجی Q فلیپفلاپ اول هستند. به همین ترتیب پایههای 7، 10، 5 و 9 به ترتیب ورودیهای K ،J، سیگنال ساعت و خروجی Q فلیپفلاپ دوم هستند. همچنین پایههای 4 و 11 تغذیه و زمین آیسی هستند و پایههای 2 و 6 نیز به منظور Reset کردن فلیپفلاپها بدون توجه به وضعیت منطقی سیگنالهای منطقی در ورودیهای آنها به کار میروند.

مشخصات برخی از آیسیهای فلیپفلاپ JK در جدول زیر نشان داده شده است.

| توصیف آیسی | خانواده آیسی | شماره آیسی |

| دو فلیپ فلاپ JK با ورودی پاک کردن | LS TTL | 74LS73 |

| دو فلیپ فلاپ JK با ورودی پاک کردن و set کردن | LS TTL | 74LS76 |

| دو فلیپفلاپ JK با ورودی پاککردن | LS TTL | 74LS107 |

| دو فلیپفلاپ JK | Standard CMOS | 4027B |

| دو فلیپفلاپ JK حساس به لبه پایینرونده با ورودیهای پاککردن و Set کردن | LS TTL | 74LS112 |

| دو فلیپفلاپ JK حساس به لبه بالارونده | LS TTL | 74LS109 |

اگر این مطلب برای شما مفید بوده است، آموزشهای زیر نیز به شما پیشنهاد میشوند:

- مجموعه آموزشهای مهندسی الکترونیک

- آموزش مدارهای منطقی (طراحی دیجیتال)

- مجموعه آموزش نرم افزارهای مهندسی برق

- آموزش مدار منطقی (مرور – تست کنکور ارشد)

- آموزش منطق ترکیبی — مجموعه مقالات جامع وبلاگ فرادرس

- منطق دیجیتال — از صفر تا صد

- گیت OR — به زبان ساده

^^

سلام .میتونید در رسم یک شمارنده 0تا 9 با استفاده از فلیپ فلاپ jk راهنمایی کنید؟؟

مطالب بسیار عالیست. ممنون از سایت خوبتون