فلیپ فلاپ SR – از صفر تا صد (+ دانلود فیلم آموزش رایگان)

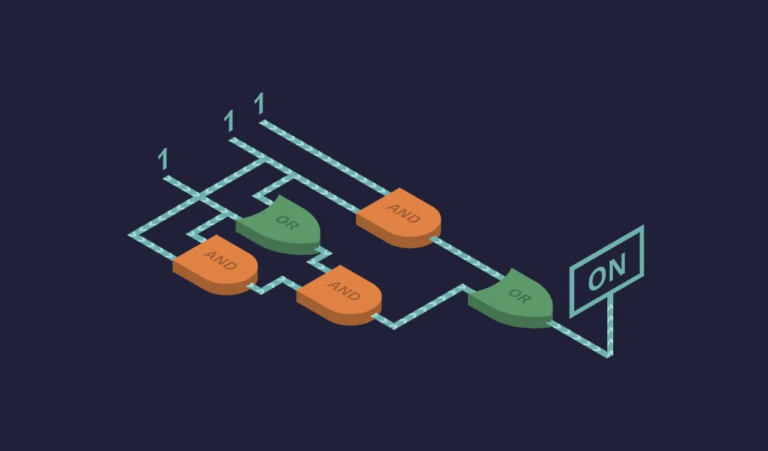

فلیپ فلاپ SR یا مدار بایاستابل، یکی از اساسیترین قطعاتی است که ساخت حافظههای کامپیوتری را ممکن ساخت. فلیپ فلاپها همچنین در ساخت بسیاری از مدارات منطقی ترتیبی کاربرد دارند. دو گیت منطقی که به صورت داخلی به یکدیگر متصل شدهاند، فرم ساده مدارات فلیپ فلاپی را تشکیل میدهند که خروجی آنها دارای دو حالت پایدار است. زمانی که مدار توسط یک پالس ورودی مناسب به یکی از این حالتها تغییر وضعیت مییابد، تا هنگامی که یک پالس ورودی دیگر به آن وارد نشود و یا منبع تغذیه از مدار قطع نشود، آن وضعیت را حفظ میکند. به همین دلیل، مدار به عنوان یک لچ بایاستابل (Bi-stable Latch) نیز شناخته میشود. در این مطلب به بررسی فلیپ فلاپهای نوع SR میپردازیم.

فیلم آموزشی نگهدار SR

فلیپ فلاپ SR میتواند به عنوان یک حافظه یک بیتی در نظر گرفته شود؛ زیرا پالس ورودی را حتی بعد از عبور آن، نگه میدارد. انواع مختلف از فلیپ فلاپها را میتوان با استفاده از گیتهای منطقی ساخت. در بین گیتهای منطقی مختلف، گیتهای NAND و گیتهای NOR تطبیقپذیرتر هستند و در بین این دو نیز استفاده از گیتهای NAND بسیار رایجتر است.

زیرا علاوه بر اینکه یک گیت عمومی (Universa) است و اکثر توابع منطقی استاندارد را توسط آن میتوان ایجاد کرد، قیمت بسیار پایینی هم دارد. سایر انواع فلیپ فلاپها که بسیار پر کاربرد هستند، فلیپ فلاپهای JK و فلیپ فلاپهای D و نیز فلیپ فلاپ نوع T هستند.

فلیپ فلاپ SR

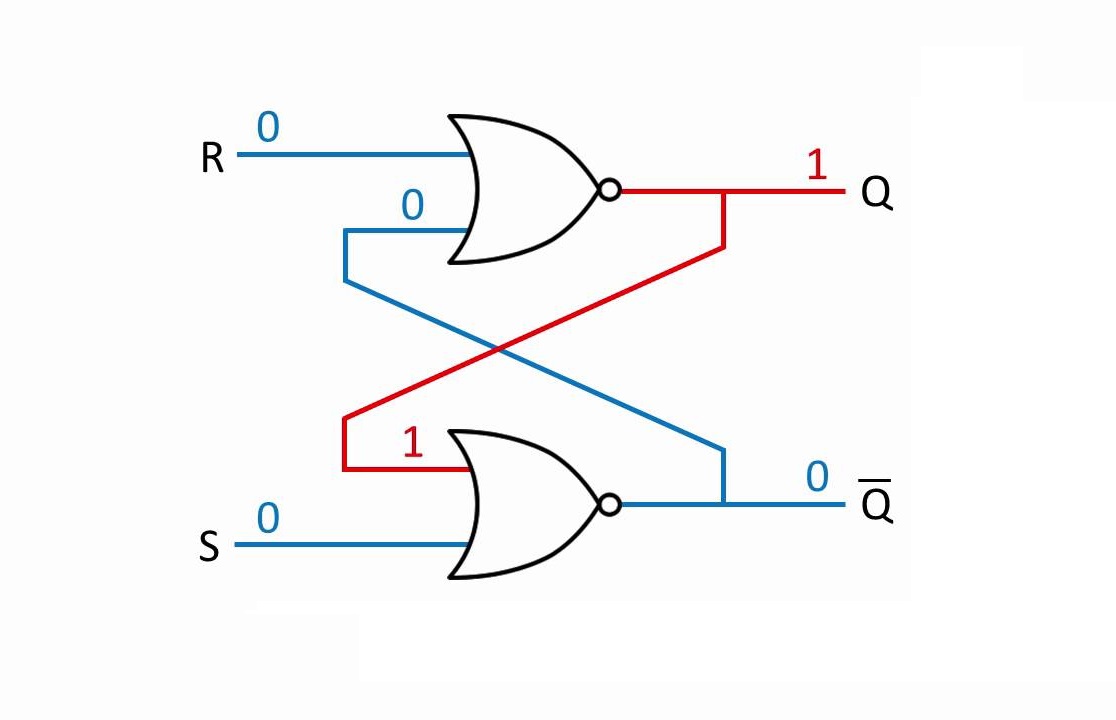

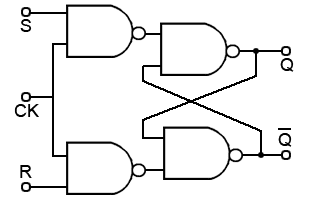

فلیپ فلاپ SR یا فلیپ فلاپ Set-Reset، یکی از ساده ترین مدارات منطقی ترتیبی است و از دو گیت منطقی NAND تشکیل شده است که مطابق شکل زیر به یکدیگر متصل شدهاند.

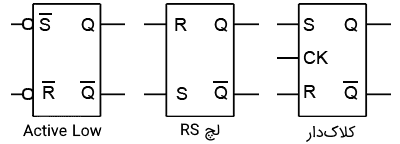

توجه کنید که خروجی هر گیت، به فرم فیدبک مثبت (Positive Feedback) و یا کوپل متقاطع (Cross-Coupling) به یکی از ورودیهای گیت دیگر متصل شده است. مدار دارای دو ورودی Active Low است که توسط نمادهای و نشان داده میشوند و نماد خط روی حروف R و S نشاندهنده عملگر NOT منطقی است. و نیز دو خروجی این مدار هستند.

جدول درستی این مدار در زیر آورده شده است و نشان میدهد که با اعمال پالس صفر و یک به ورودیهای آن، وضعیت خروجیها به چه صورت خواهند بود.

| توضیحات | |||||

| ست کردن خروجی Q به مقدار یک منطقی | ۰ | ۱ | ۱ | ۰ | ۱ |

| عدم تغییر (باقی ماندن خروجی در سطح یک) | ۰ | ۱ | ۱ | ۱ | ۲ |

| ریست شدن خروجی به مقدار صفر | ۱ | ۰ | ۰ | ۱ | ۳ |

| عدم تغییر (باقی ماندن خروجی در سطح صفر) | ۱ | ۰ | ۱ | ۱ | ۴ |

| هر دو خروجی در سطح یک منطقی (حالت غیر مجاز) | ۰ | ۱ | ۰ | ۰ | ۵ |

| خروجی تعریف نشده | ؟ | ؟ | ۱ | ۱ | ۶ |

در ابتدا با اعمال پالس صفر به ورودی ، خروجی در یک منطقی تنظیم میشود. حال با بازگرداندن حالت ورودی به یک منطقی، وضعیت خروجی تغییری نخواهد کرد و در واقع پالس صفر توسط مدار به خاطر سپرده میشود. حال مدار را با اعمال پالس صفر به ورودی ریست میکنیم. با بازگرداندن مقدار به یک منطقی، حالت صفر در ورودی به خاطر سپرده میشود.

مشکلات فلیپ فلاپهای SR

مشکلات خاصی در فلیپ فلاپهای SR به عنوان پایهایترین فرم مدارات فلیپ فلاپی، وجود دارند. برای شرایط یک تا چهار در جدول بالا، خروجی معکوس خروجی است. اما در ردیف پنجم در این جدول، هر دو ورودی دارای حالت صفر منطقی هستند. این ورودیها باعث میشوند هر دو خروجی و در حالت یک منطقی قرار گیرند. از آنجا که این خروجیها دیگر در منطق متضاد با یکدیگر نیستند، در عمل این حالت مجاز نیست، حتی اگر به لحاظ تئوری امکانپذیر باشد.

در ردیف ششم از جدول، هر دو ورودی در حالت یک منطقی قرار دارند و در نتیجه خروجیها در حالت نامشخص (Indeterminate) قرار میگیرند. این حالت به این معنی است که اگرچه خروجیها در منطق مخالف با یکدیگر هستند، اما دقیقا مشخص نیست که آیا خروجی در حالت صفر منطقی قرار دارد یا یک منطقی. توجه کنید که در غیاب پالسهای ورودی، هر دو ورودی در حالت یک منطقی قرار دارند و این مورد مشکلی ندارد؛ زیرا خروجیها در وضعیتی هستند که از حالت آخرین ورودی به خاطر سپردهاند. حالت نامشخص یا حالت منطقی نامعین فقط زمانی اتفاق میافتد که ورودیها با هم از حالت 0 و 0 به حالت 1 و 1 تغییر یابند. در عملکرد عادی باید از وقوع این حالت خودداری شود. زمانی که ابتدا منبع تغذیه را اعمال کنیم، احتمال زیادی دارد که این حالت اتفاق بیفتد و منجر به نتایج غیرقطعی شود، اما فلیپ فلاپ با اعمال پالس به هر کدام از ورودیها عملکرد عادی خواهد داشت.

بنابراین فلیپ فلاپ SR یک حافظه ساده تک بیتی است. اگر ورودی S به منطق صفر برده شود و سپس مجددا به منطق یک تغییر یابد، هر پالس صفر دیگری که در ورودی اعمال شود، فاقد تاثیر روی خروجی خواهد بود.

صافکننده کلیدزنی

در فلیپ فلاپهای SR، پالسهای تکراری در ورودیهای یا ، بعد از اینکه پالس اولیه، خروجی Q را ست و یا ریست کرد، دیگر به سادگی نادیده گرفته میشوند. به دلیل همین ویژگی، فلیپ فلاپهای SR برای کاربردهایی نظیر صافکننده ولتاژ کلیدزنی مورد استفاده قرار میگیرند.

هر گاه یک شی متحرک با شی ثابتی برخورد کند، شی متحرک شروع به نوسان (Bounce) میکند. تیغههای کنتاکتور در کلیدها نیز از این قاعده مستثنی نیستند. اگرچه این برخورد در کلید بسیار کوچک و نیز حرکات در ابعاد کم انجام میگیرد، اما هنگام بسته شدن کلید، این تیغهها تمایل دارند تا به جای این که بسته شوند و در حالت بسته باقی بمانند، ابتدا اندکی نوسان کنند. تصویر متحرک زیر نحوه وقوع این پدیده را نشان میدهند.

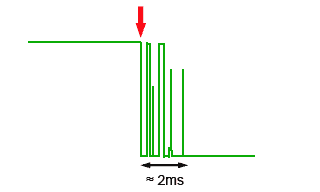

این پدیده منجر به ایجاد نوسانات بسیار سریع در شکل موج ولتاژ خروجی میشود که تا زمان کوتاهی بعد از بسته شدن کلید ادامه مییابد و در نهایت تیغههای کلید در حالت بسته به ثبات میرسند. همانطور که در شکل زیر نیز دیده میشود، تا زمان بسیار کوتاهی بعد از بسته شدن کلید (حدود 2 میلی ثانیه)، تعدادی پالسهای گذرا بسیار سریع در ولتاژ خروجی اتفاق میافتند. در تصویر، لحظه بسته شدن کلید با یک فلش قرمز مشخص شده است.

برای بسیاری از کاربردها، از این نوسانات میتوان به راحتی صرف نظر کرد. اما در مدارات دیجیتالی، صفر و یک شدنهای متوالی خروجی بعد از بسته شدن کلید، به عنوان عملهای کلیدزنی جدید شناخته میشوند. بنابراین باید حتما از وقوع این پدیده در مدارات دیجیتالی جلوگیری کرد.

مدار صافکننده ولتاژ کلیدزنی

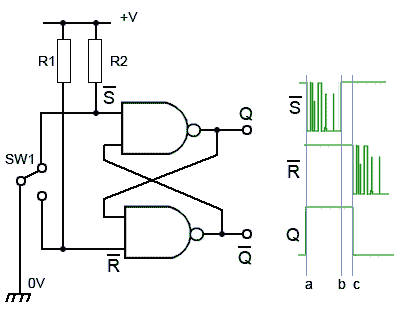

استفاده از فلیپ فلاپهای SR در حذف نوسانات ولتاژ ناشی از کلیدزنی بسیار موثر است. شکل زیر مدار مربوط به استفاده از فلیپ فلاپ SR برای تولید پالسهای صاف و تمیز را نشان میدهد.

زمانی که کلید |SW1 مسیر بالایی را به ولتاژ صفر ولت متصل میکند، ورودی از منطق یک به منطق صفر تغییر میکند و ورودی از طریق مقاومت پول آپ (Pulled Up) به منبع تغذیه یا منطق یک متصل میشود.

تا زمانی که در منطق صفر باشد (در تصویر با نقطه a نشان داده شده است.)، خروجی Q نیز در منطق یک خواهد بود و از هر پالس اضافی که به دلیل کلیدزنی به وجود آید، صرف نظر میشود.

اما قبل از این که کلید کاملا به اتصال پایینی متصل شود، زمان بسیار کوتاهی (بین لحظات b تا c) هیچکدام از ورودیهای و به ولتاژ صفر ولت متصل نیستند. در طول این زمان، ورودی به سطح یک منطقی باز میگردد، بنابراین تا زمان c هر دو ورودی در سطح یک منطقی هستند. در زمان c، ورودی R توسط کلید به ولتاژ صفر ولت متصل میشود و خروجی Q به مقدار صفر منطقی ریست میشود، در نتیجه پالس خروجی قرینه میشود.

به این روش کلیدزنی Break Before Make میگویند و اهمیت آن نسبت به روش Make Before Break در این است که در روش اول ابتدا اطمینان حاصل میشود که در بازه b تا c که بازه تغییرات است، هر دو ورودی در حالت یک منطقی قرار دارند. به این صورت از حالت غیرمجاز که در آن هر دو ورودی در حالت صفر قرار دارند، جلوگیری میشود. با استفاده از این روش میتوان اطمینان حاصل کرد که خروجیهای و هیچگاه با هم در یک حالت منطقی قرار نمیگیرند. همچنین در طول حالت گذار کلید SW1 هر دو ورودی در سطح یک منطقی قرار دارند و به همین دلیل حالت تعریفنشده در جدول درستی بالا ایجاد نمیشود؛ زیرا یکی از ورودیها همیشه در حالت منطقی صفر قرار دارد، قبل از این که هر دو ورودی به سطح یک بروند.

لچ RS

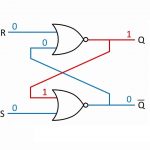

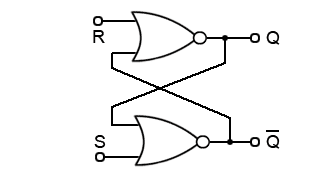

فلیپ فلاپ همچنین میتواند به عنوان مدار لچ (Latch) نیز در نظر گرفته شود؛ زیرا این ادوات میتوانند یک تغییر در ورودی خود را به خاطر بسپارند و یا اصطلاحا آن حالت را لچ کنند. در شکل زیر یک مدار لچ متداول نشان داده شده است. در این مدار ورودیهای و به ورودیهای R و S تغییر پیدا کردهاند، به این معنی که این ورودیها در مدار لچ به صورت Active High هستند. همچنین محل این ورودیها نیز تغییر کرده است و ورودی R اکنون به گیتی وارد می شود که خروجی Q دارد و ورودی S متعلق به گیتی است که خروجی آن است. دلیل این تغییرات این است که در این مدار به جای گیت NAND از گیت NOR استفاده شده است.

جدول درستی این مدار به صورت زیر است.

| توضیحات | |||||

| ست کردن خروجی Q به مقدار یک منطقی | ۰ | ۱ | ۱ | ۰ | ۱ |

| عدم تغییر (باقی ماندن خروجی در سطح یک) | ۰ | ۱ | ۰ | ۰ | ۲ |

| ریست شدن خروجی به مقدار صفر | ۱ | ۰ | ۰ | ۱ | ۳ |

| عدم تغییر (باقی ماندن خروجی در سطح صفر) | ۱ | ۰ | ۰ | ۰ | ۴ |

| هر دو خروجی در سطح یک منطقی (حالت غیر مجاز) | ۰ | ۰ | ۱ | ۱ | ۵ |

| خروجی تعریف نشده | ؟ | ؟ | ۰ | ۰ | ۶ |

ابتدا زمانی که ورودی S به سطح یک منطقی میرود، خروجی Q به مقدار یک ست میشود. این حالت حتی بعد از این که ورودی به حالت صفر منطقی بازگردد نیز در خروجی به خاطر سپرده میشود. سپس زمانی که ورودی R به یک منطقی ریست شود، خروجی Q نیز به سطح صفر منطقی ریست میشود. در سطر چهارم، بعد از این که ورودی R دوباره به حالت صفر منطقی بازگردد، حالت قبلی باز هم در خروجی Q به یاد سپرده میشود. اگر هر دو ورودی در حالت یک منطقی باشند، خروجی Q و مشابه با یکدیگر خواهند بود. این حالت در واقع غیر مجاز است. زمانی که ورودیها از حالت 1 و 1 به حالت 0 و 0 تغییر پیدا کنند، حالت خروجی قابل تضمین نخواهد بود.

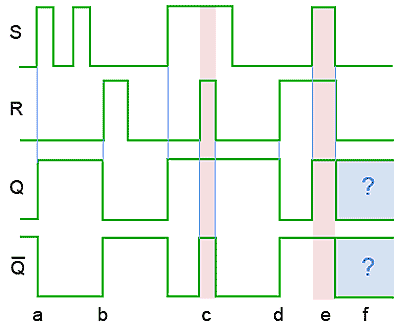

دیاگرام زمانبندی

جدول درستی گاهی اوقات راه درستی برای توصیف رفتار یک مدار ترتیبی مانند فلیپ فلاپ SR نیست. در این مواقع استفاده از دیاگرام زمانبندی ایده بهتری است: زیرا نشان میدهد حالتهای منطقی در نقاط مختلف در یک مدار در زمانهای مختلف چگونه تغیر میکنند. تصویر زیر دیاگرام زمانبندی یک لچ SR را نشان میدهد که نحوه عملکرد این لچ و نیز تغییرات منطقی ورودیهای R و S را نشان می دهد.

در زمان a، ورودی S به سطح یک منطقی میرود و خروجی Q را ست میکنند، در نتیجه تا زمان b در سطح یک منطقی باقی میماند. در این لحظه ورودی S به سطح LOW تغییر مییابد و ورودی R به سطح یک منطقی برده میشود، در نتیجه خروجی Q ریست میشود. در طول بازه c، هر دو ورودی R و S در سطح یک منطقی هستند و منجر به ایجاد حالت غیر مجازی میشوند که طی آن خروجیها هر دو در حالت HIGH قرار میگیرند. بعد از بازه c، خروجی Q تا زمان d در سطح یک باقی میماند، که در آن ورودی R به سطح یک منطقی برده میشود و خروجی Q را ریست میکند. بازه e هم مجددا جزو بازههای غیر مجاز است و در انتها، هر دو ورودی به سطح صفر منطقی میروند و منجر به ایجاد شرایط خروجی تعریف نشده در بازه f میشوند.

فلیپ فلاپ SR کلاکدار

پیکربندی دیگری از فلیپ فلاپهای SR، که به فلیپ فلاپهای SR کلاکدار معروف هستند، در شکل زیر نشان داده شده است.

با اضافه کردن دو گیت NAND دیگر به مدار فلیپ فلاپهای ساده ذکر شده در بالا، میتوان زمانبندی تغییرات خروجی را بعد از تغییر سطوح منطقی R و S، کنترل کرد. عمل کنترل کردن توسط اعمال پالس کلاک به ورودیها قابل پیادهسازی است. همچنین باید به این نکته توجه شود که ورودیها مجددا R و S نام دارند، بنابراین این مدار نیز دارای ورودیهای Active High است. به دلیل این که دو ورودی گیتهای NAND اضافی زمانی غیر فعال میشوند که ورودی کلاک در حالت LOW قرار داشته باشد، بنابراین خروجیها کاملا از ورودیها ایزوله هستند و هر حالت منطقی قبلی را به راحتی حفظ میکنند. اما زمانی که ورودی CK در حالت HIGH قرار داشته باشد، گیتهای NAND ورودی مانند معکوس کننده عمل میکنند . به عنوان مثال، یک پالس منطق یک به ورودی S اعمال میشود، اما پالس ورودی به ، ورودی طبقه دوم مدار فلیپ فلاپ SR که Active Low است، منطق صفر خواهد داشت.

مزیت اصلی پالس کلاک ورودی این است که میتوان خروجی فلیپ فلاپ را با بسیاری دیگر از مدارات و ادواتی که دارای پالس کلاک مشابهی هستند، سنکرون کرد. از این آرایش میتوان در یک حافظه ساده استفاده کرد. به عنوان مثال، با اعمال حالتهای منطقی مختلف به یک آرایه هشت فلیپ فلاپی و سپس اعمال پالس کلاک، منجر به ذخیره شدن یک بایت از اطلاعات میشود.

فرم پایهای فلیپ فلاپ SR کلاکدار، مثالی از فلیپ فلاپهای حساس به سطح (Level Triggered) است. این عبارت به این معنی است که خروجی فقط در بازه زمانی میتواند به یک سطح منطقی جدید تغییر یابد که در آن بازه پالس کلاک در سطح یک منطقی باشد. این ویژگی که ورودی فقط زمانی تغییر مییابد که پالس کلاک در سطح یک منطقی باشد، تبدیل به یکی از مشکلات این نوع مدارات شده است؛ زیرا هر تغییر در سطح منطقی ورودیها (در زمانی که سطح پالس کلاک در صفر منطقی قرار دارد) منجر به تغییر خروجیها نیز میشود. روش بهتر برای تریگر شدن در این مدارات این است که فقط در لحظات خاصی اجازه تغییر خروجیها صادر شود. میتوان با استفاده از ادوات حساس به لبه (Edge Triggered) به این هدف رسید. فلیپ فلاپهای D و نیز فلیپ فلاپهای JK نمونهای از چنین ادواتی هستند.

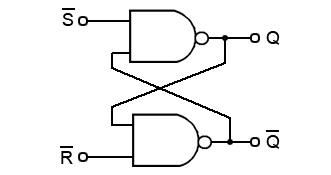

پیادهسازی گیت فلیپ فلاپهای SR با استفاده از گیتهای NAND استاندارد بسیار ساده است. اما این گیتها در پکیجهای آماده از خانواده آیسیهای LS TTL نوع 74LS279 نیز موجود است. همچنین به این نکته توجه شود که به جای ترسیم مدار شماتیک برای هر گیت تکی از این نوع فلیپ فلاپها، متداول است که نمادهای مانند شکل زیر را برای آنها ترسیم کنند.

اگر این مطلب برای شما مفید بوده است، آموزشهای زیر نیز به شما پیشنهاد میشوند:

- مجموعه آموزشهای مهندسی الکترونیک

- آموزش مدارهای منطقی (طراحی دیجیتال)

- مجموعه آموزشهای نرمافزارهای مهندسی برق

- آموزش مدار منطقی (مرور – تست کنکور ارشد)

- آموزش منطق ترکیبی — مجموعه مقالات جامع وبلاگ فرادرس

- منطق دیجیتال — از صفر تا صد

- گیت OR — به زبان ساده

^^

سلام فلیپ فلاپ با لچ چه فرقی میکنه؟

درود روزتان بخیر سرکار خانم اقایی لطفا جهت اموزش بهتر مخصوصا جهت مبتدیان مطالب را بعد از ترجمه ویرایش کنید مثلا جهت مثال چرا از همان nor استفاده نکردید و امدید از nand با ورودی not استفاده کردید که مفهوم set و reset را برای مبتدی و حتی غیر میتدی پیچیده میکنند من احساس میکنم شما بخشهایی از نسخه مرجع و خیلی توضیحات ضروری را حذف کردید .

در اینجا فرد هنوز با مفهوم ست و ری ست اشنا نشده شما بک not هم به ورودی اصافه کردید و کاملا گیجش میکنید . اموزش اگر کامل و درست نباشد خیلی بدتر از اموزش ندادن است زیرا باعث سرخوردگی و عدم اعتماد ب ه نفس میشود موفق باشید

با سلام؛

از ارائه بازخورد شما بسیار سپاسگزاریم. سعی میکنیم در آیندهای نزدیک، حتما مطالب را بازنویسی کنیم تا کاستیهایی نیز اگر وجود داشته، برطرف شوند.

با تشکر از همراهی شما با مجله فرادرس

سلام

در خصوص مدار SR سنکرون وآسنکرون چه فرقی هست به عبارت دیگه چطوری میتوان با تغییرات فلیپ فلاپ SRسنکرون میتوان یک فلیپ فلاپ آسنکرون طراحی کرد

متشکرم